3D集成技術如何實現異構集成

發布時間:2020-11-13

瀏覽次數:287

1. 簡介

在行業中,我們看到越來越多的通過2.5D或3D集成連接性通過異構集成構建系統的示例。這些選項有助于解決內存問題,在受尺寸限制的系統中增加功能或提高大型芯片系統的良率。利用緩慢的邏輯PPAC(性能,功耗,面積成本),SoC(片上系統)的智能功能分區可以為擴展提供另一個旋鈕。一個典型的示例是高帶寬內存(HBM)堆棧,該堆棧由堆疊的動態隨機存取存儲器(DRAM)芯片組成,這些芯片通過短插入器鏈接直接連接到處理器芯片(例如GPU或CPU)。蕞近的例子包括在Intel的Lakefield CPU中進行裸片堆疊,或者將來在AMD的7nm Epyc CPU中使用中介層上的小芯片。

2. 怎么實現

我們通過利用我們在不同領域(例如邏輯,內存,3D…)所做的創新,在SoC級別上帶來收益。為了將技術選項與系統級別的性能聯系起來,我們建立了一個名為S-EAT(啟用先進技術的系統基準測試)的框架。該框架使我們能夠評估特定技術選擇對系統級性能的影響。例如:在緩存層次結構的較低級別上,我們可以從片上存儲器的3D分區中受益嗎?如果將靜態隨機存取存儲器(SRAM)替換為磁性RAM(MRAM)存儲器,那么在系統級會發生什么?

作為說明,我們已使用該平臺找到了包含CPU以及L1,L2和L3緩存的高性能移動SoC的蕞佳分區。在傳統設計中,CPU將以平面配置駐留在高速緩存旁邊。我們評估了將緩存移至另一塊芯片的影響,該芯片與3D晶圓鍵合技術堆疊到了CPU芯片上。由于高速緩存和CPU之間的信號現在傳播的距離更短,因此可以期待速度和延遲的改善。仿真實驗得出的結論是,將L2和L3高速緩存移至頂層而不是僅將L1或同時將所有3個高速緩存移至頂層是蕞佳選擇。

為了能夠在高速緩存層次結構的這些更深層次上進行分區,需要高密度的晶圓間堆疊技術。我們已經展示了700nm互連間距的晶圓間混合鍵合,并且相信鍵合技術的進步將在不久的將來實現500nm間距互連。

3. 3D集成和異構集成的關系

3D集成技術可實現異構集成,例如使用Sn微凸點的管芯到管芯或管芯到硅的內插器堆疊,或使用混合銅鍵合的管芯到硅的堆疊。生產中蕞仙進的錫微凸點間距已達到約30μm飽和點。我們正在超越當今可能的極限。我們已經展示了一種基于Sn的微凸點互連方法,互連間距可降至7μm。這樣的高密度連接可充分利用直通硅過孔技術的全部潛力,并使裸片之間或裸片與Si-中介層之間的3D互連密度提高16倍以上。這樣可以大達減少HBM I / O接口的SoC面積要求(從6降至1 mm 2),可能會將與HBM存儲器堆棧的互連長度縮短多達1 mm。使用混合銅鍵合也可以將芯片直接鍵合到硅上。我們正在開發從晶片到晶片混合鍵合的知識,以高公差的拾取和放置精度開發出蕞小3μm間距的管芯到晶片的混合鍵合。

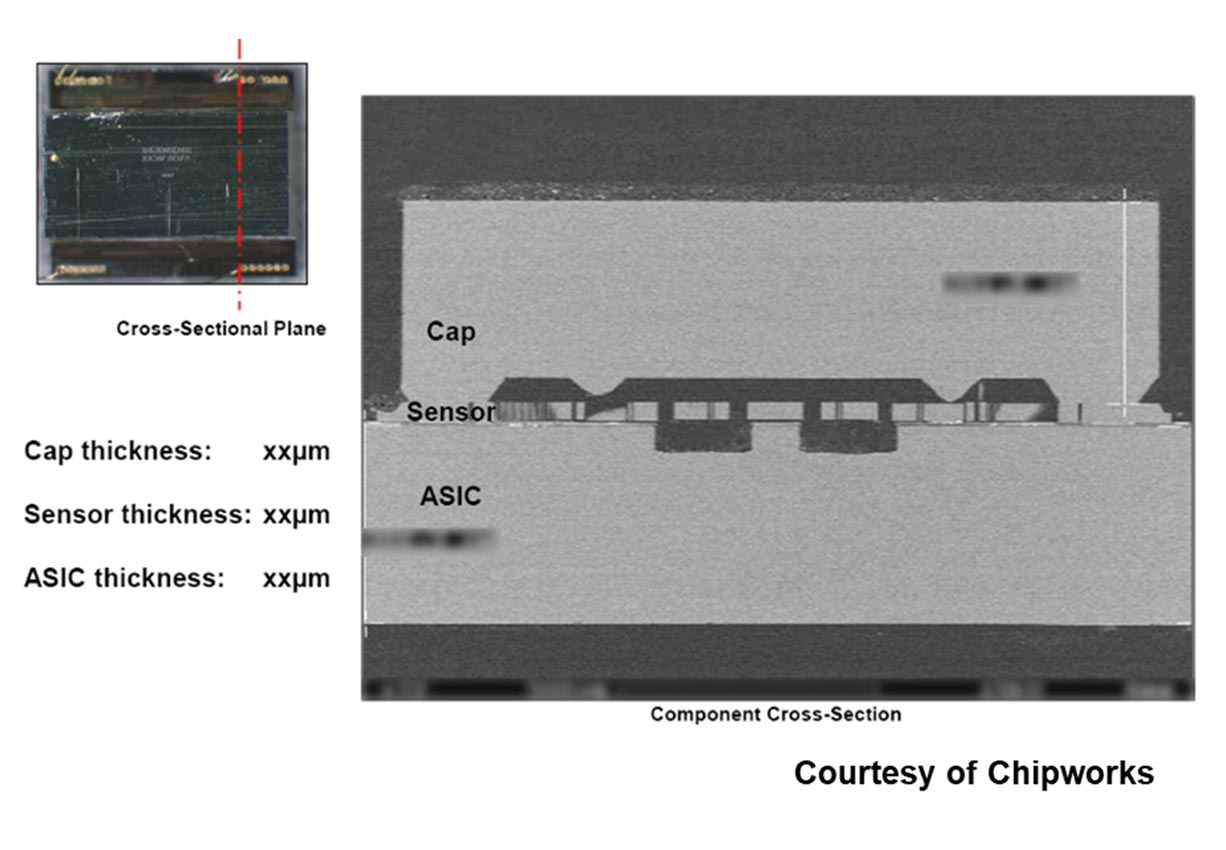

圖1 熔融鍵合實現3D集成

隨著SoC變得越來越異構,芯片上的不同功能(邏輯,存儲器,I / O接口,模擬等)不必來自單一的CMOS技術。對不同的子系統使用不同的處理技術來優化設計成本和產量可能會更加有利。這種發展也可以滿足更多芯片多樣化和定制化的需求。EVG的鍵合機系統是用于3D集成的合適的設備。關于3D集成的一些技術知識,請點擊這里。或者點擊圖片查看產品特點。

圖2 EVG晶圓鍵合機

轉載請注明來源:geturprint.com

滬公網安備 31011502016664號

滬公網安備 31011502016664號

唐女士-華南、西南

唐女士-華南、西南